# **Z02201**

# V.22BIS DATA PUMP WITH INTEGRATED AFE

**Product Specification**

PS000904-0107

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, visit <a href="https://www.zilog.com">www.zilog.com</a>.

#### **Document Disclaimer**

©2007 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

PS000904-0107 Disclaimer

# **Table of Contents**

| Features                                               | 1    |

|--------------------------------------------------------|------|

| General Description                                    | 2    |

| Pin Description                                        | 7    |

| Pin Functions                                          | 8    |

| Absolute Maximum Ratings                               | . 11 |

| Standard Test Conditions                               | . 11 |

| Environmental and power requirements                   | . 12 |

| DC Characteristics                                     | . 14 |

| AC Characteristics                                     | . 16 |

| Timing Diagrams                                        | . 18 |

| Analog Inputs: Type AI                                 | . 18 |

| Analog Outputs: Type A0                                | . 19 |

| Hardware Interface Signals                             | . 20 |

| Synchronous Serial Interface Port                      |      |

| Host Port Interface                                    |      |

| Eye Pattern Interface                                  |      |

| Technical Specifications                               |      |

| Configurations and Data Rates                          |      |

| Data Encoding                                          |      |

| Transmitted Data Spectrum                              |      |

| Transmit Levels                                        |      |

| Receiver Levels                                        |      |

| Clamping                                               |      |

| Carrier Recovery                                       |      |

| Software Interface                                     |      |

| Microprocessor Interface Register and Bit Definitions: |      |

| RAMI, RXI, and TXI Interrupts                          | . 29 |

| Interface RAM                                          |      |

| Data Pump Interface RAM Access Method                  | . 30 |

| Modem Data Pump RAM Map                                | . 32 |

| Interface RAM Definitions                              | . 34 |

| Transmitting Tones                                     | . 50 |

| Tono Dotoctors                                         | 51   |

# V.22BIS Data Pump with Integrated AFE

| Call-Progress Monitoring Using Biquad Tone Detectors | 54 |

|------------------------------------------------------|----|

| Simultaneous Transmission and Detection of Tones     | 56 |

| Dialing                                              | 57 |

| Tone Dialing                                         | 57 |

| Pulse Dialing                                        | 59 |

| Manual Handshake Procedures                          | 59 |

| Originating Modem                                    | 60 |

| Answering Modem                                      | 61 |

| Making a V.22bis Connection                          | 62 |

| Originating Modem                                    | 62 |

| Answering Modem                                      | 62 |

| Using HDLC                                           | 63 |

| HDLC Operation                                       | 63 |

| Enabling HDLC Operation                              |    |

| Transmitting                                         |    |

| Receiving                                            | 65 |

| Data Pump Firmware Version Number and Part Number    | 65 |

| Sleep Mode                                           | 66 |

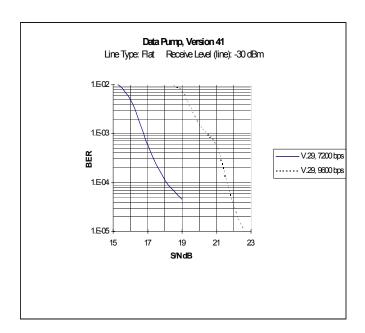

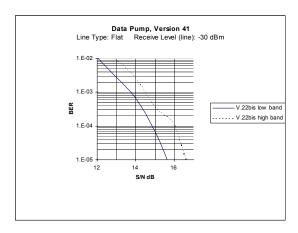

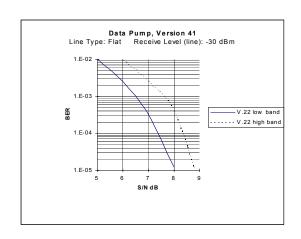

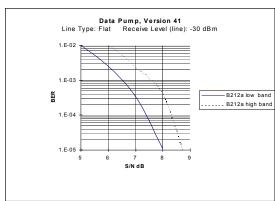

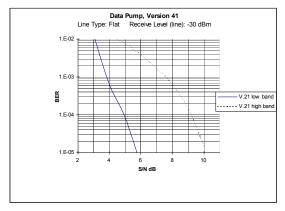

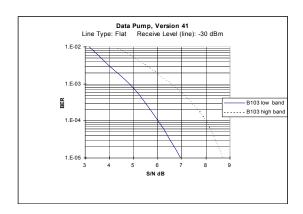

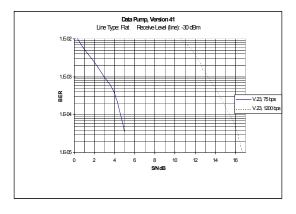

| Typical Performance Data                             | 66 |

| Example DAA                                          | 70 |

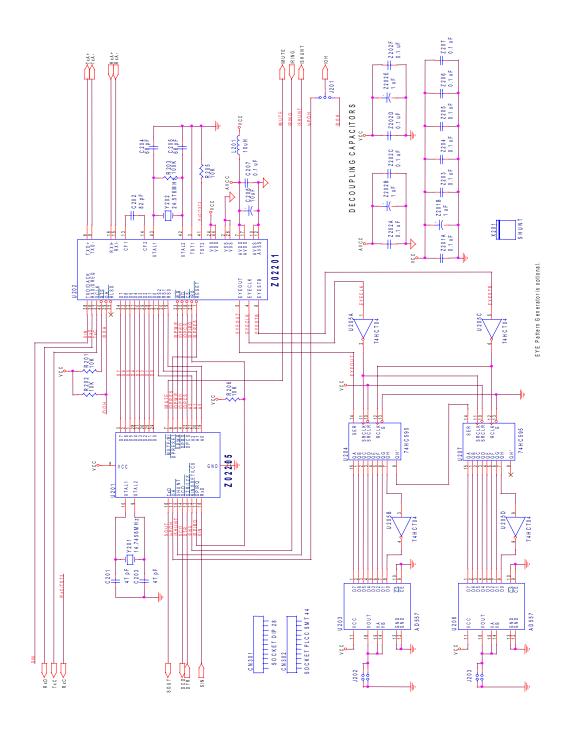

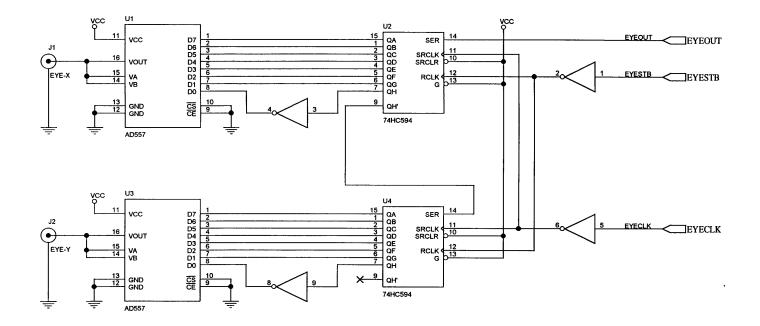

| Eye Pattern Circuit                                  | 72 |

| Package Information                                  | 73 |

| Z02201                                               |    |

|                                                      |    |

#### **Features**

| Device | Data<br>Pump | AFE        | Speed (MHz) |

|--------|--------------|------------|-------------|

| Z02201 | 16-Bit       | Integrated | 12.288      |

- Combined data pump and Analog Front-End (AFE)

- Full duplex data modem throughput to 2400 bps

- ITU V.22bis, V.23, V.22, V.21

- Bell 212A and Bell 103

- FSK (V.23 1200/75 bps, V.21/Bell 103 300 bps), DPSK (V.22/Bell 212A 1200 bps), or QAM encoding (V.22bis 2400 bps)

- Automatic handshake plus full manual control over handshake timings

- Scrambler/descrambler functions plus selectable control over internal data pump functions

- Programmable Bi-Quad tone detectors for call-progress tone detection

- Adaptive equalization to compensate for a wide variety of line conditions

- Programmable transmit attenuation and selectable receive threshold

- Fully programmable call-progress detectors, signal quality detectors, tone detectors, tone generators, and transmit signal levels which aid in rapid country qualifications

- Simultaneous tone generation and detection

- Host port allows direct parallel interface to standard 8-bit microprocessors

- HDLC framing at all speeds

- On-chip peripherals

- Full-duplex voice band AFE with 12-bit resolution

- Synchronous Serial Interface port

- Eye pattern interface

- Low power consumption: 50 mA typical

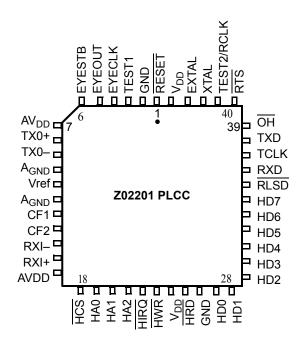

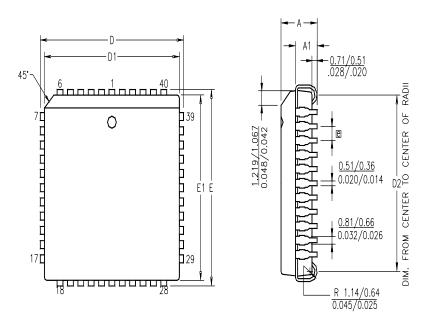

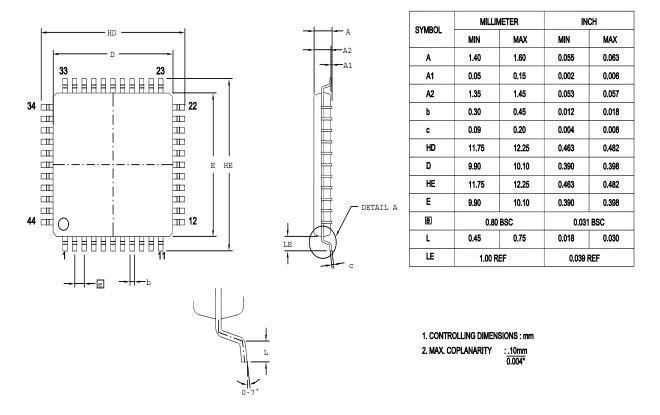

- 44-Pin PQFP and PLCC packages

- Single +5 VDC power supply

- 0 °C to +70 °C commercial temperature range

- Note: International Telecommunications Union (ITU), formerly CCITT.

## **General Description**

The Z02201 is a synchronous single-chip modem solution that provides a means to construct a V.22bis modem capable of 2400 bps full duplex over dial-up lines. The Z02201 is specifically designed for use in embedded modem applications where space, performance, and low power consumption are key requirements.

Operating over the Public Switched Telephone Network (PSTN), the Z02201 meets the modem standards for V.22bis, V.22, V.23, V.21, Bell 212A, and Bell 103.

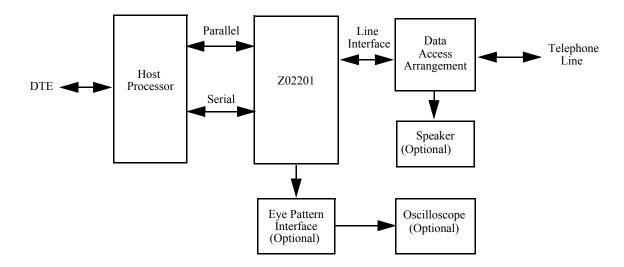

A typical modem application can be made by simply adding a control microprocessor (host), phone-line interface, and DTE interface.

The Z02201 performs HDLC framing at all speeds. This capability eliminates the requirement for an external Serial Input/Output (SIO) device for Data Terminal Equipment (DTE) in products incorporating error control.

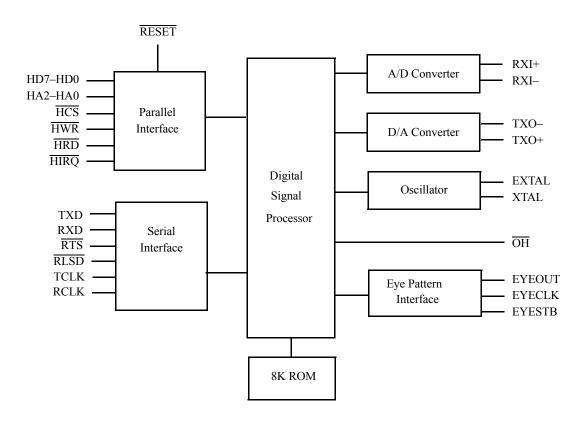

All modulation, demodulation, filtering, A/D and D/A conversion functions for transmit and receive are provided on-chip. Automatic and selectable compromise equalizers are included to optimize performance over a wide range of line types.

The Z02201 device compensates for a wide variety of adverse line conditions by using a combination of fixed link, fixed cable, and adaptive equalizers.

The Z02201 provides comprehensive selectable and programmable tone generation and detection.

All digital I/O signals are TTL compatible. The parallel interface is compatible with standard 8-bit microprocessors, allowing direct access to eight I/O registers and indirect access to the modem RAM.

The RAM access capability allows the host to retrieve diagnostic data, modem/ line status and control data, and set programmable coefficients. The serial interface is used for data transfers. All control and status information is transferred by means of the parallel interface.

The Z02201 transmit drivers and receive amplifiers can be connected directly to a Data Access Arrangement (DAA) by means of a transformer. Completing this connection reduces the external circuits to a minimum.

In addition, the Z02201 offers further system level savings by providing built-in filters for both the Transmitter Analog Output and the Receiver Analog Input, thus eliminating the need for external filtering components.

The Z02201 device operates on a single +5 VDC power supply. During periods of no traffic, the host can place the modem into SLEEP mode, reducing power consumption to less than 1 percent of full load power.

#### Z02201 V.22BIS Data Pump with Integrated AFE

Note: All signals with an overline, are active Low. For example, B/W, in which WORD is active Low; or B/W, in which BYTE is active Low.

Power connections follow conventional descriptions below:

| Connection | Circuit  | Device          |

|------------|----------|-----------------|

| Power      | $V_{CC}$ | $V_{DD}$        |

| Ground     | GND      | V <sub>SS</sub> |

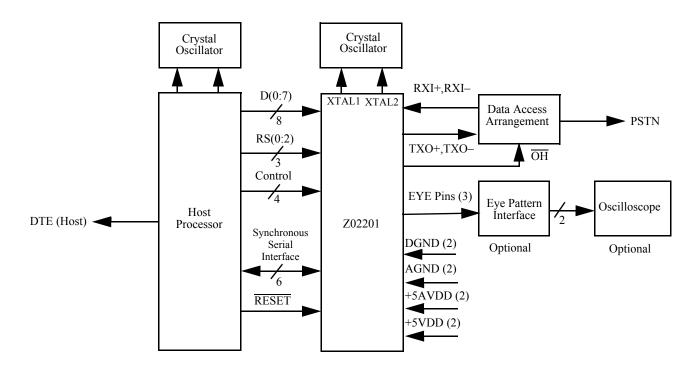

Figure 1. Z02201 Block Diagram

#### **User Information**

The ZiLOG Z02201 data pump can be selected for either parallel or serial synchronous data transfer under software control. Figure 2 indicates a block diagram of the general modem chip interface. The hardware and software configurations can be customized for a particular modem application. The parallel interface allows direct access to 7 I/O registers, indirect access to the modem RAM, and is compatible with the Z8, Z80, Z18X family, and other 8-bit microprocessors. The serial interface is used for data transfer. Controls and status information are transferred via the parallel interface. The RAM access capability allows indirect access to diagnostic data, additional status control, and programmable coefficients. The hardware and software interfaces are presented in the subsequent sections.

Figure 2. Z02201 System Block Diagram

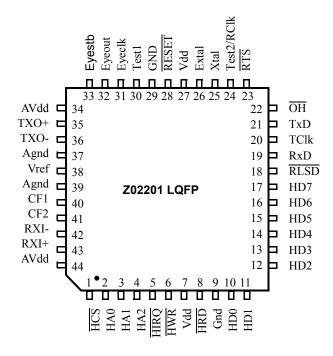

Figure 3. Z02201 44-Lead PLCC Pin Identification

Figure 4. Z02201 44-Lead LQFP Pin Identification

# **Pin Description**

Table 1. Z02201 Pin Assignments

| PLCC Pin | LQFP Pin | Signal | Direction    |

|----------|----------|--------|--------------|

| 1        | 28       | RESET  |              |

| 2        | 29       | Gnd    |              |

| 3        | 30       | Test1  | Input        |

| 4        | 31       | Eyeclk | Output       |

| 5        | 32       | Eyeout | Output       |

| 6        | 33       | Eyestb | Output       |

| 7        | 34       | AVdd   |              |

| 8        | 35       | TXO+   | Output       |

| 9        | 36       | TXO-   | Output       |

| 10       | 37       | Agnd   |              |

| 11       | 38       | Vref   | Output       |

| 12       | 39       | Agnd   |              |

| 13       | 40       | CF1    | Input        |

| 14       | 41       | CF2    | Input        |

| 15       | 42       | RXI-   | Input        |

| 16       | 43       | RXI+   | Input        |

| 17       | 44       | AVdd   |              |

| 18       | 1        | HCS    | Input        |

| 19       | 2        | HA0    | Input        |

| 20       | 3        | HA1    | Input        |

| 21       | 4        | HA2    | Input        |

| 22       | 5        | HIRQ   | Output       |

| 23       | 6        | HWR    | Input        |

| 24       | 7        | Vdd    |              |

| 25       | 8        | HRD    | Input        |

| 26       | 9        | Gnd    |              |

| 27       | 10       | HD0    | Input/Output |

| 28       | 11       | HD1    | Input/Output |

Table 1. Z02201 Pin Assignments (Continued)

| PLCC Pin | LQFP Pin | Signal     | Direction    |

|----------|----------|------------|--------------|

| 29       | 12       | HD2        | Input/Output |

| 30       | 13       | HD3        | Input/Output |

| 31       | 14       | HD4        | Input/Output |

| 32       | 15       | HD5        | Input/Output |

| 33       | 16       | HD6        | Input/Output |

| 34       | 17       | HD7        | Input/Output |

| 35       | 18       | RLSD       | Output       |

| 36       | 19       | RxD        | Output       |

| 37       | 20       | TClk       | Output       |

| 38       | 21       | TxD        | Input        |

| 39       | 22       | ОН         | Output       |

| 40       | 23       | RTS        | Input        |

| 41       | 24       | Test2/RClk | Input/Output |

| 42       | 25       | Xtal       | Output       |

| 43       | 26       | Extal      | Input        |

| 44       | 27       | Vdd        |              |

#### **Pin Functions**

HD7-HD0 Host Data Bus (Bidirectional, Active High)—HD0-HD7 constitutes an 8bit bidirectional data bus used for the transfer of control and status information.

**HCS** Host Chip Select (Input, Active Low)—When  $\overline{\text{CS}}$  is Low, data transfer between the data pump and the host is enabled. Data transfers to the data pump registers are 8 bits wide.

HWR Host Write Enable Strobe (Input, Active Low)—The write enable strobe is an active Low signal that is used to initiate a write operation to the data pump. During a write operation, data is sent to the data pump by the host via the host data bus.

HRD Host Read Enable Strobe (Input, Active Low)—The read enable strobe is an active Low signal that is used to initiate a read operation from the data pump. During a read operation, data is transferred out of the data pump by the host via the host data bus.

HIRQ Host Interrupt Request (Output, Active Low)—The HIRQ is an open-drain output that can be tied through an external pull-up resistor to the digital power

supply  $V_{DD}$ . The  $\overline{HIRQ}$  active Low data pump output can be activated when the host selects this option or requests by setting the RXIE or TXIE bits in the data pump Host Register. This pin can be connected to the host interrupt request pin to initiate host service.

RESET Reset (Input, Active Low)—The RESET signal places the device into its reset state.

HA2–HA0 Host Address (Input, Active High)—These three register select lines (pins) are used for addressing the controller-accessible internal registers of the data pump. When HCS is active, the state of the HA2–HA0 is used as the internal data pump interface register address. HA2 is the most significant bit; HA0 is the least significant bit.

RLSD Receive Line Signal Detect (Output, Active Low)—This pin indicates when an input signal has been detected.

**RXD** *Receive Data* (Output)—The data pump serial receive data is presented by the data pump to the local DTE on the RXD output.

**TCLK** *Transmit Serial Data Clock* (Output)—The serial data output clock is a synchronous data clock used to transfer serial data via synchronous serial interface between the data pump and the host. The clock frequencies are 2400, 1200, and 300 Hz, corresponding to the supported data bit rates.

**TXD** *Transmit Data* (Input)—The data pump accepts the serial transmit data from the local DTE on the TXD input when the data pump is configured to the serial transmit data mode. The serial transmit data mode is selected when the TDPM bit (bit 4) of the RAM CONTROL/DATA PUMP STATUS register (Register 6) is reset to 0

**OH** *Off Hook Relay Control* (Output, Active Low)—This pin is activated to drive a relay which engages the modem with the phone line (the modem equivalent of picking up the receiver).

RTS Request To Send (Input, Active Low)—The logical OR of this pin and the RTSP bit (bit 3 of register 4), determines the data pump mode of operation. When the result of the logical OR of these two bits is logic 1, the data pump is in transmit mode at the selected speed, thereby placing the data pump in receive mode. In STANDBY mode, the state of this pin is insignificant.

**EYECLK** *Eye Pattern Clock* (Output, Active High)—Data is valid at the rising edge of the clock. The EYECLK can be used to clock an external Digital-to-Analog (D/A) converter shift register for eye pattern display.

**EYEOUT** *Eye Pattern Data* (Output, Active High)—This pin controls the serial 16-bit eye pattern output data. The first 8 bits is the EYEX data, and the next 8-bits are the EYEY data. This data can be used for display on an oscilloscope X and Y-axis following D/A conversion.

**EYESTB** Serial Eye Pattern Strobe (Output, Active High)—This signal is used for loading an external D/A converter.

**TXO+** *Transmit Differential Analog Output Positive* (Analog Output)—The TXO+, TXO- is capable of driving a 600-ohm resistive load over a leased line or public switched telephone network via a Data Access Arrangement (DAA). The TXO- and TXO+ can be configured either as a differential or single-ended output driver.

TXO- Transmit Differential Analog Output Negative (Analog Output)—The TXO-, TXO+ is capable of driving a 600-ohm resistive load over a leased line or public switched telephone network via a Data Access Arrangement (DAA).

RXI- Receive Differential Analog Input Negative (Analog Input)—

RXI+ Receive Differential Analog Input Positive (Analog Input)—

**TEST1** *Test Pin 1* (Input, Active High)—This pin is a test pin and must be tied to digital ground.

**TEST2/RCLK** *Test Pin 2, Receive Data Clock* **(Output, Active High)**—This pin is a test pin and must be tied to digital ground through a pull-down resistor. The resistor should be Low enough to ensure this pin floats below 0.8V when the part is in the RESET state. After RESET, this pin becomes the Receive Data Clock Output. The resistor should be high enough such that the output can be driven to logic 1. This pin is a synchronous data clock used to transfer serial data between the data pump and the host. The clock frequencies are 2400, 1200, and 300 Hz corresponding to the supported data bit rates.

**Vref** *Reference Voltage* (Output, Active High—An internally generated reference voltage.

**XTAL** *Crystal* (Output, Active High)—Crystal oscillator connection. This pin must be left open if an external clock is used instead of a crystal. The data pump chip can be connected to an external crystal circuit consisting of 24.576-MHz (parallel resonant) crystal, a resistor, and two capacitors.

**EXTAL External Clock/** *Crystal* (Input, Active High)—Crystal oscillator connection. An external clock can be input to the Z02280 on this pin when a crystal is not used. The oscillator input is not a TTL level (see DC characteristics in Table 4).

**CF1** and **CF2** *Integration Capacitor Pins 1* and **2** (Analog Input)—Connect an 82pF capacitor between CF2 and CF1 to complete the internal feedback integration filter for improved Analog-to-Digital (A/D) conversion performance.

GND Digital ground-0 Volts-

V<sub>DD</sub> Digital Power-5 Volts-

AV<sub>DD</sub> Analog Power-5 Volts-

AGND Analog Ground-0 Volts-

## **Absolute Maximum Ratings**

**Table 2. Absolute Maximum Ratings**

| Symbol                 | Description             | Min  | Max  | Units |

|------------------------|-------------------------|------|------|-------|

| V <sub>CC</sub>        | Supply Voltage          | -0.3 | +7.0 | V     |

| T <sub>OPR</sub> (com) | Operating Temperature 0 |      | +70  | °C    |

| T <sub>STG</sub>       | Storage Temperature     | -65  | +150 | °C    |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This rating is a stress rating only. Operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Standard Test Conditions**

The DC Parameters were tested as per Table 6. The Z02201 tester has active loads which are used to test the loading for  $I_{OH}$  and  $I_{OR}$

**Available operating temperature range is:** where: S = Standard Temperature Range

$$S = 0^{\circ}C$$

to  $+70^{\circ}C$

#### **Voltage Supply Range:**

$$+4.5 \text{ V} \le \text{ V}_{CC} \le +5.5 \text{ V}$$

All AC parameters assume a load capacitance of 100 pF. Add 10 ns delay for each 50 pF increase in load up to a maximum of 150 pF for the data bus, and 100 pF for address and control lines.

## **Environmental and power requirements**

The modem power and environmental requirements are indicated in Table 3 and Table 4. Table 5 provides the crystal specifications.

**Table 3. Power Requirements**

| Voltage                           | Current Typical<br>@ 25°C | Current<br>Maximum @ 0°C |  |  |

|-----------------------------------|---------------------------|--------------------------|--|--|

| +5 V <sub>DC</sub> ,<br>Operating | 50 mA                     | <=100 mA                 |  |  |

| +5 V <sub>DC</sub> , Sleep        | 25 μΑ                     | <=125 μΑ                 |  |  |

Note: All voltages are  $\pm 5\%$  DC and must have ripple less than 0.1V peak to peak. If switching supply is used, the frequency may be between 20 kHz and 150 kHz. No component of the switching frequency should be present outside of the supply greater than 500  $\mu$ V peak.

**Table 4. Environmental Requirements**

| Parameter                                              | Value           |

|--------------------------------------------------------|-----------------|

| Ambient Temperature Under Bias (Commercial Temp Range) | 0°C to +70°C    |

| Storage Temperature                                    | –65°C to +150°C |

| Voltage on Any Pin to V <sub>SS</sub>                  | -0.3V to +7V    |

| Power Dissipation                                      | 250 mW          |

| Soldering Temperature 0.5 sec                          | +230°C          |

Table 5. Z02201 Crystal Specifications

| Parameter                           | Value             |

|-------------------------------------|-------------------|

| Temperature Range (Commercial)      | 0°C to +70°C      |

| Nominal Frequency @ 25°C            | 24.576 MHz        |

| Frequency Tolerance @ 25°C          | ±20 ppm           |

| Temperature Stability @ 0°C to 70°C | ±25 ppm           |

| Calibration Mode                    | Parallel Resonant |

| Shunt Capacitance                   | 7 pF max.         |

Table 5. Z02201 Crystal Specifications (Continued)

| Parameter                                          | Value        |

|----------------------------------------------------|--------------|

| Load Capacitance                                   | 32 ± 0.3 pF  |

| Drive Level                                        | 1.0 mW max.  |

| Aging, per Year Max.                               | ± 5 ppm      |

| Oscillation Mode                                   | Fundamental  |

| Series Resistance                                  | 60 ohms max. |

| Max. Frequency Variation with 28.8 or 35.2 pF load | ±30 ppm      |

## **DC Characteristics**

**Table 6. TDC Pin Characteristics**

| Parameter                                   | Description                  | Min                  | Тур       | Max                  | Units | Test Conditions             |

|---------------------------------------------|------------------------------|----------------------|-----------|----------------------|-------|-----------------------------|

| Pin Types I and I/O: Input and Input-Output |                              |                      |           |                      |       |                             |

| V <sub>IH</sub>                             | Input High Voltage           | 2                    | _         | V <sub>CC</sub> +0.3 | V     |                             |

| V <sub>IL</sub>                             | Input Low Voltage            | 0                    | _         | 8.0                  | V     |                             |

| IL                                          | Input Leakage Current        | -10                  | _         | 10                   | μΑ    | GND <v0<v<sub>DD</v0<v<sub> |

| Pin Types O                                 | and IO: Output and Input-C   | utput                |           |                      |       |                             |

| $V_{OH}$                                    | Output High Voltage          | 2.4                  | _         | _                    | V     | I <sub>OH=</sub> –200 μA    |

| $V_{OL}$                                    | Output Low Voltage           | 0                    | _         | 0.4                  | V     | I <sub>OI=</sub> –2.2 mA    |

| I <sub>OZ</sub>                             | Tri-state Leakage Current    | -10                  | _         | 10                   | μΑ    | GND <v0<v<sub>DD</v0<v<sub> |

| Pin Types I-                                | PU and I-PD: Input with Inte | rnal Pull-up         | /Pull-dow | n Resistor           |       |                             |

| $V_{IH}$                                    | Input High Voltage           | 2                    |           | V <sub>CC</sub> +0.3 | V     | I <sub>OI=</sub> –2.2 mA    |

| V <sub>IL</sub>                             | Input Low Voltage            | 0                    |           | 8.0                  | V     |                             |

| I <sub>IL</sub>                             | Input Current                | -10                  |           | 10                   | μΑ    | GND <v0<v<sub>DD</v0<v<sub> |

| Pin Type XI:                                | Crystal Input                |                      |           |                      |       |                             |

| $V_{IH}$                                    | Input High Voltage           | V <sub>DD</sub> x0.8 |           | V <sub>DD</sub>      | V     |                             |

| $V_{IL}$                                    | Input Low Voltage            | 0                    |           |                      |       |                             |

| Pin Type O-                                 | OD: Output with Open-Drain   | 1                    |           |                      |       |                             |

| $V_{OL}$                                    | Output Low Voltage           | 0                    | _         | 0.4                  |       | I <sub>OI</sub> =2.2 mA     |

| I <sub>OZ</sub>                             | Tri-state Leakage Current    | -10                  | _         | 10                   | μΑ    | GND <v0<v<sub>DD</v0<v<sub> |

| Pin Type XC                                 | ): Crystal Output            |                      |           |                      |       |                             |

| V <sub>OH</sub>                             | Output High Voltage          | V <sub>DD</sub> –1   |           | $V_{DD}$             | V     | I <sub>OH</sub> =1.0 mA     |

| V <sub>OL</sub>                             | Output Low Voltage           | 0                    |           | 1                    | V     | I <sub>OI</sub> =–1.0 mA    |

| Pin Type Al:                                | Analog Input                 |                      |           |                      |       |                             |

| $V_{DC}$                                    | Input Bias Offset            | V <sub>REF</sub> -15 | $V_{REF}$ | V <sub>REF</sub> +15 | mV    |                             |

| IL                                          | Input Current                | -100                 | _         | 100                  | μА    |                             |

| C <sub>IN</sub>                             | Input Capacitance            | _                    | 10        | _                    | pF    |                             |

| R <sub>IN</sub>                             | Input Resistance             |                      | 20        |                      | Kohm  |                             |

| Pin Type AC                                 | ): Analog Output             |                      |           |                      |       |                             |

**Table 6. TDC Pin Characteristics (Continued)**

| Parameter         | Description            | Min                         | Тур              | Max                        | Units | Test Conditions |

|-------------------|------------------------|-----------------------------|------------------|----------------------------|-------|-----------------|

| V <sub>O</sub>    | Analog Output Voltage  | V <sub>REF</sub> –<br>1.163 | V <sub>REF</sub> | V <sub>REF</sub><br>+1.163 | mV    |                 |

| V <sub>OFF</sub>  | Output DC Offset       | V <sub>REF</sub> –40        | V <sub>REF</sub> | V <sub>REF</sub> +40       | mV    |                 |

| R <sub>O</sub>    | Output Resistance      | _                           | 0.8              | _                          | Ohm   |                 |

| C <sub>O</sub>    | Output Capacitance     | _                           | 10               | _                          | pF    |                 |

| Z <sub>I</sub>    | Load Impedance         | 400                         | 600              | Infinite                   | Ohm   |                 |

| Pin Type PW       | /R: Power and Ground   |                             |                  |                            |       |                 |

| $V_{DD}$          | Digital Supply Voltage | 4.75                        | 5                | 5.25                       | V     | Voltage         |

| GND               | Digital Ground         | _                           | _                | 0                          | _     |                 |

| AV <sub>DD</sub>  | Analog Supply Voltage  | V <sub>DD</sub>             | $V_{DD}$         | $V_{DD}$                   | V     |                 |

| AGND              | Analog Ground          | GND                         | GND              | GND                        | V     |                 |

| I <sub>DD1</sub>  | Digital Supply Current | _                           | 45               | 90                         | mA    | Operating       |

| I <sub>ADD1</sub> | Analog Supply Current  | _                           | 5                | 10                         | mA    | Operating       |

| I <sub>DD2</sub>  | Digital Supply Current | _                           | 20               | 100                        | μΑ    | Sleep Mode      |

| I <sub>ADD2</sub> | Analog Supply Current  | _                           | 5                | 25                         | μΑ    | Sleep Mode      |

## **AC Characteristics**

## **Timing Diagrams**

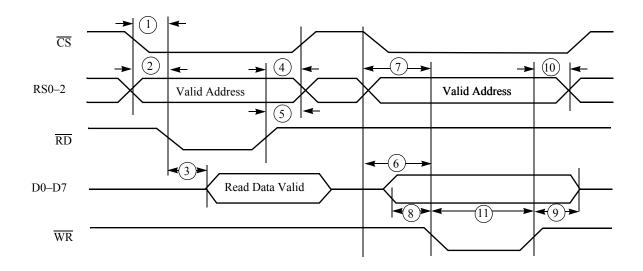

Figure 5. Microprocessor Interface Read/Write Diagram

**Table 7. Microprocessor Interface Timing**

| Description                     | Parameter | Min | Тур | Max | Units |

|---------------------------------|-----------|-----|-----|-----|-------|

| Read Timing                     |           |     |     |     |       |

| HA0–2 and HCS to HRD Setup Time | 1         | 0   | _   | -   | ns    |

| HA0-2 to HRD Setup Time         | 2         | 0   | _   | -   | ns    |

| HRD to Data Access Time         | 3         | _   | 25  | 85  | ns    |

| HRD Data Hold                   | 4         | 0   | 10  | _   | ns    |

| HA0-2 and HCS Hold From HRD     | 5         | 0   | _   | _   | ns    |

| Write Timing                    |           |     |     |     |       |

| HA0–2 and HCS to HWR Setup Time | 6         | 70  | _   | _   | ns    |

| HCS to HWR Setup Time           | 7         | 70  | _   | _   | ns    |

| Data to HWR Setup Time          | 8         | 0   | _   | _   | ns    |

| HWR Data Hold                   | 9         | 10  | _   | _   | ns    |

| HA0–2 and HCS Hold from HWR     | 10        | 10  | _   | _   | ns    |

**Table 7. Microprocessor Interface Timing (Continued)**

| Description       | Parameter | Min | Тур | Max | Units |

|-------------------|-----------|-----|-----|-----|-------|

| HWR Pulse Width   | 11        | 25  | _   | _   | ns    |

| Reset Timing      |           |     |     |     |       |

| Reset Pulse Width |           | 1.0 | _   | _   | μs    |

| Reset Rise Time   |           |     | _   | 100 | ns    |

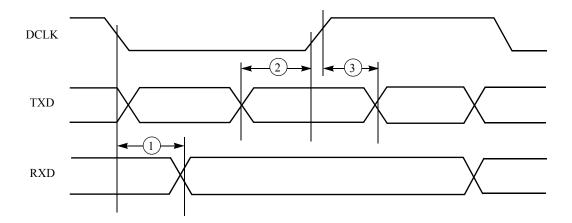

Figure 6. Serial Port Timing Diagram

**Table 8. Serial Interface Timing**

| Description               | Parameter | Min | Тур | Max | Units |

|---------------------------|-----------|-----|-----|-----|-------|

| RXD Data Valid Delay Time | 1         | _   | 12  | -   | ns    |

| TXD Data Setup Time       | 2         | 100 | -   | -   | ns    |

| TXD Data Hold Time        | 3         | 100 | _   | _   | ns    |

## **Timing Diagrams**

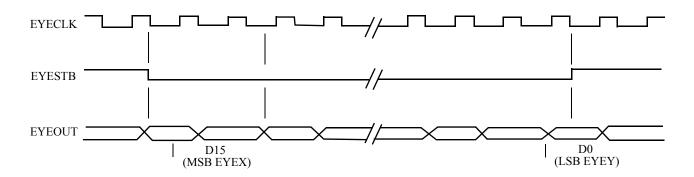

Figure 7. Eye Pattern Port Timing Diagram

**Table 9. Analog Characteristics Table**

| Description                                     | Parameter | Min | Тур  | Max  | Units |

|-------------------------------------------------|-----------|-----|------|------|-------|

| Input impedance of transformer interface        | 1         | 400 | 1200 | -    | Ohm   |

| 3 dB point of interface                         | 2         | 21  | 26.5 | 32.5 | kHz   |

| External integration capacitance Type NPO (COG) | 3         | 73  | 82   | 90   | pF    |

# **Analog Inputs: Type Al**

Table 10. Analog Inputs, Type Al

| AC Characteristics                        | Sym               | Min | Тур | Max             | Units |

|-------------------------------------------|-------------------|-----|-----|-----------------|-------|

| Input Impedance (DC to V <sub>REF</sub> ) | Z <sub>IN</sub>   | 15K | 25K | -               | Ω     |

| Power Supply Rejection                    | P <sub>SRRi</sub> | 40  | _   | _               | dB    |

| Input Current                             | l <sub>i</sub>    | -80 | _   | 80              | μА    |

| Idle Channel Noise<br>(3950 Hz Bandwidth) | I <sub>CNi</sub>  | _   | _   | <del>-</del> 72 | dBm   |

| Signal to Distortion                      | S <sub>TDi</sub>  | 30  | -   | _               | dB    |

The characteristics below are provided for information only. They are not tested

#### except in the functional test vectors.

| Characteristics                                   | Sym                | Min    | Тур  | Max    | Units |

|---------------------------------------------------|--------------------|--------|------|--------|-------|

| Input Capacitance                                 | C <sub>IN</sub>    | -      | 10   | -      | pF    |

| Input Bias                                        | V <sub>DCOFF</sub> | _      | +2.5 | -      | V     |

| Analog Input Voltage<br>(Peak Differential), (23) | V <sub>PKI</sub>   | -2.362 | -    | +2.362 | V     |

| Analog Input Voltage<br>(Per RXI+. RXI- Pin)      | V <sub>PKIP</sub>  | -1.181 | _    | +1.181 | V     |

## **Analog Outputs: Type A0**

Table 11. Analog Inputs Type A0

| AC Characteristics                        | Sym               | Min | Тур         | Max        | Units |

|-------------------------------------------|-------------------|-----|-------------|------------|-------|

| Power Supply Rejection                    | P <sub>SRRO</sub> | 40  | -           | _          | dB    |

| Signal to Distortion                      | S <sub>TD0</sub>  | 35  | -           | _          | dB    |

| Idle Channel Noise<br>(3950 Hz Bandwidth) | I <sub>CNO</sub>  | -   | -           | <b>-72</b> | dBm   |

| Out of Band Noise                         | N <sub>qo</sub>   |     |             |            | dBm   |

| 4–8 kHz                                   | _                 | -   | -20         |            | dBm   |

| 8–12 kHz                                  | _                 | -   | -40         |            | dBm   |

| 12 kHz and Above in 4 kHz Bandwidths      | _                 | -   | <b>–</b> 55 |            | dBm   |

| Characteristics                                 | Sym  | Min    | Тур  | Max    | Units |

|-------------------------------------------------|------|--------|------|--------|-------|

| Output Impedance                                | Zout | _      | 0.80 | _      | Ω     |

| Output Capacitance                              | Cout | _      | 10   | _      | pF    |

| Analog Output Voltage (peak differential), (24) | Vpko | -2.375 | -    | +2.375 | V     |

| Load Impedance (25)                             | ZI   | 400    | 600  | _      | _     |

## **Hardware Interface Signals**

The Z02201 interface consists of the Synchronous Serial Interface Port, 8-bit Host Microprocessor Interface, Eye Pattern Interface, Voice Band AFE, System Signals, and Overhead Signals. The Z02201 functional interconnect diagram is indicated in Figure 8. Any signal that is active Low is represented by a line over the signal name.

Figure 8. Modem Functional Interconnect Diagram

## **Synchronous Serial Interface Port**

The Synchronous Serial Interface Port provides no parallel-to-serial/serial-to-parallel conversion hardware. The synchronous serial interface port consists of six signal pins as shown in Table 12.

**Table 12. Synchronous Serial Interface Port**

| -    |                            |

|------|----------------------------|

| Pin  | Signal Name                |

| TxD  | Transmit Data              |

| RxD  | Receive Data               |

| RTS  | Request To Send            |

| RLSD | Receive Line Signal Detect |

| TCLK | Transmit Data Clock        |

| RCLK | Receive Data Clock         |

#### **Host Port Interface**

The host parallel port interface consists of 15 signal pins: 8-bit bidirectional data bus pins (HD7–HD0), 3-bit Address bus (HA2–HA0), four control lines, which include the HoST READ (HRD), HOST WRITE (HWR), HOST CHIP SELECt (HCS), and HOST INTERRUPT REQUEST (HIRQ). Multiple interrupt sources are provided in the Z02201, each of which can be masked under host control.

The host parallel interface allows the host to access the data pump RAM address and data bits, transmit and receive data, control the RAM and status bits, and read data pump status bits. The host can access eye pattern functions, transmit and receive tones, and access adaptive equalizer coefficients in modem-type applications.

The host parallel interface is compatible with standard 8-bit microprocessors, which include the Z8 and Z80 bus.

#### **Eye Pattern Interface**

The eye pattern interface consists of three pins: EYE PATTERN DATA (EYEOUT), EYE PATTERN CLOCK (EYECLK), and EYE PATTERN STROBE (EYESTB). Sixteen bits of data are serially transmitted via EYEOUT, under control of EYESTB and EYECLK. The first byte is the X-coordinate and the second byte is Y-coordinate of the sample. The least significant bit is presented first for both the X and Y coordinates. A schematic of an eye pattern circuit is found in Figure 16 at the end of this specification.

The EYE PATTERN DATA, EYEOUT, outputs a serial bit stream containing data for display of the eye pattern on an oscilloscope after D/A conversion. 8 bits of the X-axis data and 8 bits of the Y-axis are output as a single 16-bit data stream with the

X-axis data first. EYEOUT is synchronous with the rising edge of EYECLK. EYEOUT is valid only while the EYESTB is Low. Data is shifted out MSB first.

Data on eyeout is shifted out on each rising edge of the 1.536MHz EYECLK. EYE-OUT data is valid on the following edge of the EYE PATTERN CLOCK, EYECLK.

The EYEOUT data is valid when the EYE PATTERN STROBE, EYESTB, is Low. EYE-STB changes state on the rising edge of EYECLK.

#### **Technical Specifications**

#### **Configurations and Data Rates**

Table 13 provides the selectable options, supported data rate, baud rate, and the modulation method.

#### **Tone Generation and Tone Detection**

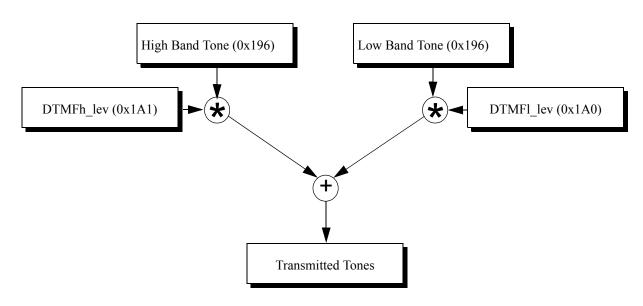

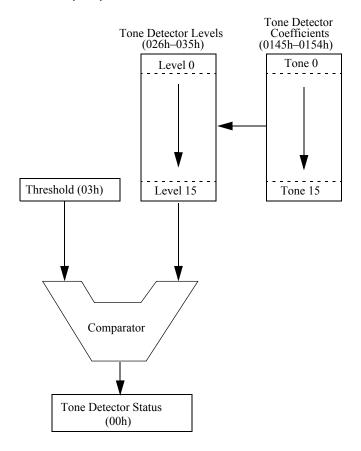

The Z02201 provides comprehensive and flexible tone generation and detection, including all tones required to establish a circuit connection and to setup and control a communication session. The tone generation furnishes the DTMF tones for PSTN auto dialing, and the supervisory tones for call establishment. The tone detection provides support for call-progress monitoring. The detector can also be user-programmed to recognize up to 16 tones.

## Data Encoding

The data encoding for the Z02201 meets both ITU–T recommendations and Bell standards.

**Table 13. Selectable Configurations**

| Configuration <sup>1</sup> | Modulation <sup>2</sup> | Carrier Freq. | Data Rate<br>(bps) | Symbol<br>Rate (baud) | Bits Per<br>Symbol | Constellation Points |

|----------------------------|-------------------------|---------------|--------------------|-----------------------|--------------------|----------------------|

| V.22 bis 2400              | QAM                     | 1200/2400     | 2400               | 600                   | 4                  | 16                   |

| V.22 bis 1200              | DPSK                    | 1200/2400     | 1200               | 600                   | 2                  | 4                    |

| V.22 1200                  | DPSK                    | 1200/2400     | 1200               | 600                   | 2                  | 4                    |

| V.23 1200/75               | FSK                     | 1700/420      | 1200/75            | 1200/75               | 1                  | _                    |

#### Notes:

- 1. Configuration is selected through the RAM location Config.

- 2. QAM=Quadrature Amplitude Modulation FSK=Frequency Shift Keying, DPSK=Dual Phase Shift Keying

**Table 13. Selectable Configurations (Continued)**

| V.21      | FSK  | 1080/1750 | 300  | 300 | 1 | _ |

|-----------|------|-----------|------|-----|---|---|

| Bell 212A | DPSK | 1200/2400 | 1200 | 600 | 2 | 4 |

| Bell 103  | FSK  | 1170/2125 | 300  | 300 | 1 | _ |

#### Notes:

- 1. Configuration is selected through the RAM location Config.

- 2. QAM=Quadrature Amplitude Modulation FSK=Frequency Shift Keying, DPSK=Dual Phase Shift Keying

#### **Transmitted Data Spectrum**

The transmitted data spectrum, with compromise equalization disabled, is shaped in the baseband by the finite impulse response (FIR) filter. Table 14 reflects the spectrum characteristics.

**Table 14. Spectral Shaping**

| V.221200sqrt 75% Raised Cosine at 600 baudV.22bis2400sqrt 75% Raised Cosine at 600 baud | Mode    | Carrier Freq | Spectral Power Shaping Function    |

|-----------------------------------------------------------------------------------------|---------|--------------|------------------------------------|

| V.22bis 2400 sqrt 75% Raised Cosine at 600 baud                                         | V.22    | 1200         | sqrt 75% Raised Cosine at 600 baud |

| ·                                                                                       | V.22bis | 2400         | sqrt 75% Raised Cosine at 600 baud |

Note: The carrier and the spectral shaping are selected automatically according to the configuration.

#### **Transmit Levels**

The transmit output level of the Z02201 is programmable in 1 dBm decrements from –6 dBm to –43 dBm. With a default value of –10 dBm, the Z02201 is measured differentially across pins TX0+ and TX0– with a sinusoidal waveform.

Note: To avoid saturation, the Tx level should be set to -6 dBm or lower by the host. If a higher transmit level is required, additional op amps may be added during operation.

#### **Receiver Levels**

The timing recovery circuit can track a  $\pm 0.01\%$  (100 ppm) frequency error in the associated transmit timing source with less than 1.0 dB degradation in performance.

#### Clamping

Received Data (RXD) is clamped to a constant mark whenever RLSD is OFF.

#### **Carrier Recovery**

The recovery circuit can track a  $\pm 7$  Hz frequency offset in the receiver carrier with less than 1.0 dB degradation in performance.

#### Software Interface

Note: This section refers to the Version 0x48 of the datapump firmware. For various versions of the datapump and the differences in firmware refer to the addendum of the product specification.

The host microprocessor communicates with the Z02201 via the parallel microprocessor bus interface. Access is provided to a set of seven 8-bit Interface Registers, and through these registers, to Z02201 RAM memory locations. This interface allows the host to request modem status information and receive data, control the configuration, and load data for transmit. Table 15 is the Parallel Interface Register map.

Table 15. Parallel Interface Register Map

| Function                | Register<br>Number | RS2-0<br>b2b1b0 | MSB<br>Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1 | LSB<br>Bit 0 | Access<br>Method |

|-------------------------|--------------------|-----------------|--------------|-------|-------|--------|----------|-------|-------|--------------|------------------|

| RAM Access<br>Low       | 0                  | 000             |              |       | 1     | RAMDL  |          |       |       |              | R/W              |

| RAM Access<br>High      | 1                  | 001             |              |       |       | RAMDH  |          |       |       |              | R/W              |

| RAM Access<br>Address   | 2                  | 010             |              |       |       | RAMAL  |          |       |       |              | W                |

| Parallel Data           | 3                  | 011             |              |       |       | DATAP  |          |       |       |              | R/W              |

| RAM Control<br>& Status | 4                  | 100             | TXIE         | RXIE  | RAMIE | TPDM   | RTSP     | RAMRW | RAMRQ | RAMAH        | R/W              |

| Modem<br>Status         | 5                  | 101             | TXI          | RXI   | RAMI  | DPBUSY | Reserved | RTRND | CDET  | RES          | R                |

| HDLC                    | 7                  | 111             | 0            | 0     | 0     | 0      | 0        | TEND  | RXERR | EOF          | R/W              |

#### **Microprocessor Interface Register and Bit Definitions:**

Reg0, Reg1 RAMDL, RAMDH—DATA PUMP RAM DATA REGISTERS—In this case, RAMDL is the least significant byte, and RAMDH is the most significant byte. After a data pump RAM read operation has completed, these registers contain the requested data. When a data pump RAM write operation is started, these registers contain the data written to data pump RAM.

Reg2 RAMAL—DATA PUMP RAM DATA ADDRESS—When a data pump RAM read or write operation is started, this byte contains the lower 8 bits of the RAM address. Register 4 (RAMAH) is the high bit of the RAM address.

Reg3 DATAP—DATA PUMP PARALLEL DATA—This register contains data transferred to or from the remote modem during the parallel modem (see register Register 4, bit 4). At any reset, when Config register bits 0–6 (MODE) is 0 (STANDBY), the data pump places its firmware version number in register DATAP.

| Bit | 7    | 6    | 5     | 4    | 3    | 2     | 1     | 0     |

|-----|------|------|-------|------|------|-------|-------|-------|

|     | TXIE | RXIE | RAMIE | TPDM | RTSP | RAMRW | RAMRQ | RAMAH |

Table 16. REG4: RAM Control Register

| SYMBOL        | POSITION                | NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAMAH         | REG 4, bit 0            | RAM Address High Bit. The most significant bit of the data pump RAM address. This bit is set to 1 when accessing a data pump RAM address that is greater than 255, or set to 0 for any value below 255.                                                                                                                                                       |

| RAMRQ         | REG 4, bit 1            | Data Pump RAM Access Request Bit. Set this bit to 1 to request a read or write of the data pump RAM. The data pump sets this bit to 0 when the request has been fulfilled.                                                                                                                                                                                    |

| RAMRW         | REG 4, bit 2            | Data Pump RAM Read/Write Bit. Set this bit to 0 to request a read of the data pump RAM or a 1 to request a write of data pump RAM.                                                                                                                                                                                                                            |

| RTSP          | REG 4, bit 3            | Register Request to Send Bit. A logical OR operation is executed using the value of the hardware RTS signal received by the data pump on the RTS pin. The host sets RTS or RTSP to 1 to inform the data pump the host is transmitting data. To control the data pump using the RTS signal, set RTSP to 0. To control the data pump using RTSP, hold RTS High. |

| TPDM          | REG 4, bit 4            | Select Parallel Data Mode. Setting this bit selects the parallel data mode. Resetting it selects the serial data mode.                                                                                                                                                                                                                                        |

| Note: All the | e bits in this register | (REG 4) default to logic 0 at power-up or after reset sequences are completed.                                                                                                                                                                                                                                                                                |

Table 16. REG4: RAM Control Register (Continued)

| SYMBOL        | POSITION                | NAME AND DESCRIPTION                                                                                                                                        |

|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAMIE         | REG 4, bit 5            | RAM Interrupt Enable Bit. Setting this bit allows the data pump to interrupt the host when a RAM read/write request has been completed.                     |

| RXIE          | REG 4, bit 6            | Receive Data Interrupt Enable Bit, Parallel Data Mode Only. This bit, when set, causes the data pump to generate an interrupt whenever the RXI bit is set.  |

| TXIE          | REG 4, bit 7            | Transmit Data Interrupt Enable Bit, Parallel Data Mode Only. This bit, when set, causes the data pump to generate an interrupt whenever the TXI bit is set. |

| Note: All the | e bits in this register | (REG 4) default to logic 0 at power-up or after reset sequences are completed.                                                                              |

| Bit | 7   | 6   | 5    | 4      | 3        | 2     | 1    | 0   |

|-----|-----|-----|------|--------|----------|-------|------|-----|

|     | TXI | RXI | RAMI | DPBUSY | Reserved | RTRND | CDET | RES |

Table 17. REG5: Data Pump Status Register

| SYMBOL   | POSITION     | NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RES      | REG 5, bit 0 | Data Pump in RESET Mode. This bit is set whenever the data pump is in RESET mode because of a hardware reset or power-on. The data pump sets RES to 0 when it completes the reset cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CDET     | REG 5, bit 1 | Carrier Detect. The data pump sets CDET to 1 when it enters any data mode and is ready to transmit data. The data pump sets CDET to 0 during retrains (see Reg5, bit 2, RTRND), and when no signal is detected from the remote modem. See locations RLSDOnThresh and RLSDOffThresh for more information. CDET is inverted and reflected on the data pump's RLSD pin. If CDET is 1, RLSD is Low (asserted). At any reset, or when the host sets Config register, bits 0–6 (MODE) to 0 (STANDBY), the data pump sets CDET to 0.                                                                                                                                                                  |

| RTRND    | REG 5, bit 2 | Retrain Detect, 2400 bps (V.22bis data mode only). The Retrain sequence is detected when this bit is set. The data pump has detected a retrain request sequence from the remote modem.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Reserved | REG 5, bit 3 | Reserved bit location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DPBUSY   | REG 5, bit 4 | Data Pump Busy. This bit is set whenever the data pump starts transmitting data and RTSP is 1. When the link is to be terminated, setting RTSP to 0 causes this bit to be reset after the data pump has finished transmitting the most recent data in its internal buffers. When this bit has been reset, it is safe to set Config. register, bits 0–6 (MODE) to standby mode (0) and hang up the telephone, terminating the connection. This bit also indicates when digits are being dialed during timed dialing operation. At any reset, or when the host sets Config register, bits 0–6 (MODE) to 0 (STANDBY) the data pump sets DPBUSY to 0. This bit is not valid during HDLC operation. |

| RAMI     | REG 5, bit 5 | Data Pump RAM Interrupt Status. This bit is set when the data pump has processed a RAM read/write request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXI      | REG 5, bit 6 | Receive Interrupt Status. This bit is set when the data pump is in parallel data transfer mode (TPDM is 1) and the data pump has written a new octet to the DATAP register. A read from the DATAP register clears this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TXI      | REG 5, bit 7 | Transmit Interrupt Status. This bit is set when the data pump is in parallel data transfer mode (TPDM is 1) and the data pump has read the DATAP register. A write to the DATAP register clears this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Note: The RXI bit is set to 1 after the reset sequences. All other bits in this register (Reg. 5) default to 0 at power up or after reset sequences are completed.

| Bit | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0   |

|-----|---|---|---|---|---|------|-------|-----|

|     | 0 | 0 | 0 | 0 | 0 | TEND | RXERR | EOF |

Table 18. REG7: HDLC Register

| SYMBOL | POSITION           | NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOF    | REG 7, bit 0       | Receive End of Frame. The data pump sets EOF to 1 when an HDLC frame has been completely received (that is, when frame data has been received and a closing HDLC flag or HDLC Abort condition is received). If the frame was correctly received, the data pump also sets Reg5, bit 1 (RXERROR) to 0, Reg5, bit 6 (RXI) to 1, and DATAP to 7EH. See Reg7, bit 1 (RXERROR) for a description of CRC errors and HDLC Aborts. EOF reflects whether the current register DATAP value indicates the end of receipt of an HDLC frame. When the first data byte of the next HDLC frame is received, or if an HDLC ABORT condition is received when no HDLC frame data was received, the data pump sets EOF to 0. This condition may occur only 8 bit times after the data pump sets EOF to 1. |

| RXERR  | REG 7, bit 1       | Receive Error. If an HDLC frame contains a CRC error, or an HDLC Abort condition is received, the data pump sets RXERROR to 1, Reg5, bit 6 (RXI) to 1, and DATAP to the value of 7EH or FFH. If the frame had a CRC error, DATAP has the value of 7EH. If an HDLC Abort condition was received, DATAP is FFH. RXERROR reflects whether the current register DATAP contains an error. When the first data byte of the next HDLC frame is received, the data pump sets RXERROR to 0. This condition may occur only 8 bit times after the data pump set RXERROR to 1.                                                                                                                                                                                                                    |

| TEND   | REG 7, bit 2       | Transmit End of Frame. The data pump sets TEND to 1 when it closes an HDLC frame that is transmitted. The data pump sets TEND to 0 after transmitting the CRC bytes, when it starts transmitting the closing flag of the HDLC frame. The data pump closes an HDLC frame when the host does not provide data to transmit (see DATAP) in time to be included in the HDLC frame.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0      | REG 7,<br>bits 3–7 | Unused. Set these bits to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Notes:

- 1. All the bits in this register (REG 7) default to 0 at power up or after reset.

- 2. All undefined bits of this register are reserved. The host writes a 0 to all reserved bit positions when writing this register. The host ignores the reserved bits when reading this register.

**Reg7 Data Pump Register 7—**These bits represent the state of HDLC frames when the data pump is in the HDLC FRAMING mode. These bits are valid only if BUFC-TRL. bit 7 (HDLC) is 1. The host should refrain from writing Reg7 to avoid changing

the values of bit fields set by the data pump. Bits not defined above are reserved or not available for use.

The host reads register Reg7 immediately before DATAP. The two CRC checksum bytes in received HDLC frames are provided to the host.

At any reset, or when the host sets Config register, bits 0-6 (MODE) to 0 (STANDBY) the data pump sets TEND to 0, RXERROR to 0, and EOF to 0.

## RAMI, RXI, and TXI Interrupts

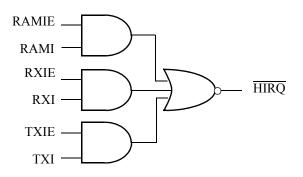

The three most significant bits in the RAM Control and data pump status registers define the interrupt masks for RAMI, RXI, and TXI. A logical AND operation is performed with the RAMIE, RXIE, and TXIE enable bits of the RAM Control register and the corresponding interrupt bits in the DATA PUMP STATUS register. A logical OR operation is performed on the outputs driving the HIRQ pin, providing an interrupt to the host interrupt (See Figure 9).

Figure 9. Host Interrupt Circuit Diagram

#### Interface RAM

The interface RAM is used by the data pump for normal operations. All writes to the interface RAM should be Read-Modify-Write, where only the bits that must be changed are affected. All undocumented bits are reserved and must be left intact.

- Notes: 1. Data pump RAM reads or writes requires approximately 0.1 msec to complete.

- Data pump RAM writes take effect at different times, depending upon the location being written to. During data modes, writes typically take effect at the end of the next baud period. During other modes of operation, writes take effect in 0.1 msec.

- 3. Writing Reg4, for example, to set Reg4, bit 7 (TXIE) to 0 in an interrupt handler while waiting for the data pump to set Reg4, bit 1 (RAMRQ) to 0 in the background, may cause unwanted side effects. Setting Reg4, bit 1 (RAMRQ) to 1 may cause the data pump to repeat the read/write request if the data pump had just set Reg4, bit 1 (RAMRQ) to 0; however, setting Reg4, bit 1 (RAMRQ) to 0 may abort the RAM read/write request.

## **Data Pump Interface RAM Access Method**

To write to the data pump RAM:

1. Write data to RAMDL & RAMDH.

- 2. Write the lower 8 bits of the address of the data pump RAM location to register RAMAL.

- 3. With one write operation to register R4, set the high bit of the data pump RAM address in R4, RAMAH, set R4, bit 2 (RAMRW) to 1, and set R4, bit 1 (RAMRQ) to 1.

- 4. Wait until the data pump sets R4, bit 1 (RAMRQ) to 0.

To read from data pump RAM:

- 1. Write the lower 8 bits of the address of the data pump RAM location to register RAMAL.

- 2. With one write operation to register R4, set the high bit of the data pump RAM address in R4, RAMAH, set R4, bit 2 (RAMRW) to 0, and set R4, bit 1 (RAMRQ) to 1.

- 3. Wait until RAMRQ is reset to 0 by the data pump or until RAMIE is set to 1.

- 4. Read data from RAMDL and RAMDH.

Reads and writes to the data pump RAM may require 105  $\mu$ s to complete.

# **Modem Data Pump RAM Map**

Table 19. Modem Data Pump RAM Map

| Mnemonic        | Address (Hex) | Access Mode | Description                                     |

|-----------------|---------------|-------------|-------------------------------------------------|

| Config          | 01FF          | R/W         | Data Pump Configuration                         |

| Trnctrl         | 01FE          | R/W         | Training Control                                |

| Bufctrl         | 01FD          | R/W         | Buffer Control                                  |

| ToneStatus      | 01FC          | R/W         | DTMF and Tone Control Status                    |

| Dpctrl          | 01FA          | R/W         | Data Pump Miscellaneous Controls                |

| MStatus         | 01F7          | R/W         | Modem Control and Status                        |

| EQMMaxThresh    | 01F6          | R/W         | MSE Maximum Threshold                           |

| RLSDOffThresh   | 01F5          | R/W         | RLSD Off Threshold                              |

| RLSDOnThresh    | 01F4          | R/W         | RLSD On Threshold                               |

| CONN_Mode       | 01F0          | R/W         | Connection Speed After Handshake is<br>Complete |

| Notch           | 01A2-01A6     | R/W         | Notch Filter Coefficients                       |

| DTMFh_lev       | 01A1          | R/W         | DTMF High Band Transmit Level                   |

| DTMFI_lev       | 01A0          | R/W         | DTMF Low Band Transmit Level                    |

| ToneGenA        | 0191          | R/W         | Tone Generator A                                |

| ToneGenB        | 0196          | R/W         | Tone Generator B                                |

| TxLevel         | 0185          | R/W         | Modem Transmit Level                            |

| Seq3Count       | 18E           | R/W         | Dial Timer Inter-Pulse Count                    |

| Seq2Count       | 18D           | R/W         | Dial Timer Off Count                            |

| Seq1Count       | 18C           | R/W         | Dial Timer On Count                             |

| BiquadA         | 0155-015E     | R/W         | Biquad A Coefficient                            |

| BiquadB         | 015F-0168     | R/W         | Biquad B Coefficient                            |

| DTD0-DTD15      | 0145–0154     | R/W         | Tone Detector Coefficients                      |

| EQMlev          | 092           | R/W         | Eye Quality Monitor Level                       |

| BiQuadOffThresh | 052           | R/W         | Biquad Detectors Off Point                      |

| BiQuadOnThresh  | 051           | R/W         | Biquad Detectors On Point                       |

Table 19. Modem Data Pump RAM Map (Continued)

| Mnemonic         | Address (Hex) | Access Mode | Description                   |

|------------------|---------------|-------------|-------------------------------|

| DTD0Lev-DTD15Lev | 026–035       | R/W         | Tone Detector Levels          |

| DTDThresh        | 03            | R/W         | Tone Detector Threshold       |

| DTDStatus        | 00            | R/W         | Discrete Tone Detector Status |

### **Interface RAM Definitions**

**Table 20. Modem Data Pump Word Definitions**

| Register & Addre (hex) | ess         | Default<br>Value | Function and Explanation                                                                                                                                                                                             |

|------------------------|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Config                 | Config 01FF |                  | Data pump Config register                                                                                                                                                                                            |

|                        |             | b15              | Unused. Set this bit to 0.                                                                                                                                                                                           |

|                        |             | b14              | ORG (Set Originate Mode: all modes) If ORG is 1, the modem is in Originate Mode. Otherwise, it is in answer mode. Be sure to set ORG before or at the same time as Config register, bits 0–6 (MODE), not afterwards. |

|                        |             | b13              | ERROR (Data Pump Error: all modes) This bit is set to 1 when the data pump detects an internal error condition such as an invalid Config code. The host should reset the data pump.                                  |

|                        |             | b12              | RESERVED                                                                                                                                                                                                             |

|                        |             | b11              | RESERVED                                                                                                                                                                                                             |

|                        |             | b10              | MCUCTRL (Manual Handshake: V.22/V.22bis/B212A) This bit allows the host to control the handshake process in V.22bis. (See Manual Handshake Procedures on page 59 for more information).                              |

|                        |             | b9               | RESERVED                                                                                                                                                                                                             |

|                        |             | b8               | SRESET (Soft Reset: all modes) Set this bit to soft reset the data pump. The data pump sets SRESET to 0 when the software reset completes.                                                                           |

|                        |             | b7               | Unused. Set this bit to 0.                                                                                                                                                                                           |

Table 20. Modem Data Pump Word Definitions (Continued)

| Register & Address (hex) | Default<br>Value | Function and Explanation                                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                          | b0-6             | MODE (Data Mode Configuration: selects a mode) Selects the data pump operation mode. All modes unlisted below should be considered Reserved. The host should read MODE, one time after writing it, to allow the data pump enough time to begin operation in the new mode. Setting MODE to 0 (STANDBY) starts the IDLE mode of operation, not the power-saving SLEEP mode. |  |  |

|                          |                  | Data Mode Specified                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                          |                  | 0 Standby                                                                                                                                                                                                                                                                                                                                                                 |  |  |